文章编号: 1001 - 9014(2016)06 - 0641 - 04

DOI:10.11972/j.issn.1001-9014.2016.06.001

## 60 nm T-shaped-gate InAlN/GaN HFETs with $f_{\rm T}$ & $f_{\rm max}$ of 170 & 210 GHz

LV Yuan-Jie, FENG Zhi-Hong\*, ZHANG Zhi-Rong, SONG Xu-Bo, TAN Xin, GUO Hong-Yu, YIN Jia-Yun, FANG Yu-Long, CAI Shu-Jun

(National Key Laboratory of Application Specific Integrated Circuit (ASIC), Hebei Semiconductor Research Institute, Shijiazhuang 050051, China)

**Abstract**: Scaled InAlN/GaN heterostructure field-effect transistors (HFETs) on sapphire substrate with high unity current gain cut-off frequency ( $f_{\rm T}$ ) and maximum oscillation frequency ( $f_{\rm max}$ ) were fabricated and characterized. In the device, scaled source-to-drain distance ( $L_{\rm sd}$ ) of 600 nm was realized by employing nonalloyed regrown n<sup>+</sup>-GaN Ohmic contacts. Moreover, a 60-nm T-shaped gate was fabricated by self-aligned-gate technology. A high drain saturation current density ( $I_{\rm ds}$ ) of 1.89 A/mm @  $V_{\rm gs}$  = 1 V and a peak extrinsic transconductance ( $g_{\rm m}$ ) of 462 mS/mm were obtained in the scaled InAlN/GaN HFETs. In addition, from the small-signal RF measurements, the values of  $f_{\rm T}$  and  $f_{\rm max}$  for the device with 60-nm gate were extrapolated to be 170 GHz and 210 GHz at the same bias. To our knowledge, they are the highest values of  $f_{\rm T}$  and  $f_{\rm max}$  for the domestic InAlN/GaN HFETs.

**Key words:** InAlN/GaN, heterostructure field-effect transistors (HFET), unity current gain cut-off frequency  $(f_{\text{T}})$ , maximum oscillation frequency  $(f_{\text{max}})$

PACS: 85.30. De, 71.55. Eq, 85.30. Tv, 78.55. Cr

# 基于 60 nm T 型栅 $f_{\rm T}$ & $f_{\rm max}$ 为 170 & 210 GHz 的 InAlN/GaN HFETs 器件

吕元杰, 冯志红\*, 张志荣, 宋旭波, 谭 鑫, 郭红雨, 尹甲运, 房玉龙, 蔡树军 (河北半导体研究所 专用集成电路国家级重点实验室,河北 石家庄 050051)

摘要:基于蓝宝石衬底 InAlN/GaN 异质结材料研制具有高电流增益截止频率  $(f_T)$  和最大振荡频率  $(f_{max})$  的 InAlN/GaN 异质结场效应晶体管 (HFETs). 基于再生长  $n^+$  GaN 欧姆接触工艺实现了器件尺寸的缩小,有效源漏间距  $(L_{sd})$  缩小至 600 nm. 此外,采用自对准栅工艺制备 60 nm T 型栅. 由于器件尺寸的缩小,在  $V_{gs}=1$  V时,器件最大饱和电流  $(I_{ds})$  达到 1.89 A/mm,峰值跨导达到 462 mS/mm. 根据小信号测试结果,外推得到器件的  $f_T$  和  $f_{max}$  分别为 170 GHz 和 210 GHz,该频率特性为国内 InAlN/GaN HFETs 器件频率的最高值.

关 键 词:InAlN/GaN;异质结场效应晶体管(HFETs);电流增益截止频率 $(f_T)$ ;最大振荡频率 $(f_{max})$

中图分类号:TN385 文献标识码:A

### Introduction

Lattice-matched InAlN/GaN heterostructure field-effect transistors (HFETs) have attracted great attention in the past several years because of their high two-dimensional electron gas (2DEG) density with an ultra-thin barrier, and potential reliability advantages<sup>[1-2]</sup>. Compared with AlGaN/GaN heterostructure, the strong spontaneous polarization in InAlN/GaN heterostructure not

only leads to a high drain current, but also effectively suppresses the short channel effects (SCEs) due to the ultra-thin InAlN gate layer. The InAlN/GaN heterostructure has been proposed as an ideal alternative for device scaling to improve the RF characteristics. Moreover, since without piezoelectric polarization in the lattice-matched InAlN/GaN heterostructure, the defects can be reduced, offering a solution to strain-related device reliability.

In recent years, outstanding improvements in the

Received date: 2016-01-02, revised date: 2016-09-28 收稿

Foundation items: Supported by National Natural Science Foundation of China (61306113)

收稿日期:2016-01-02,修回日期:2016-09-28

Biography: LV Yuan-Jie (1985-), male, Shandong, China, Ph. D. Research fields focus on GaN-based electronic devices. E-mail: yuanjielv@163.com

\* Corresponding author: E-mail: ga917vv@163.com

frequency performance of InAlN/GaN HFETs have been achieved. Lee et~al employed oxygen plasma treatments to reduce RF transconductance ( $g_{\rm m}$ ) collapse, and fabricated a 30 nm gate-length InAlN/GaN HFET with unity current gain cut-off frequency ( $f_{\rm T}$ ) of 245 GHz  $^{[3]}$ . They then introduced InGaN back barrier to suppress the SCEs, and improved the value of  $f_{\rm T}$  to be 300 GHz  $^{[4]}$ . Using regrown Ohmic contacts, Yue et~al reduced the source-to-drain distance ( $L_{\rm sd}$ ) to 270 nm, and reported a high  $f_{\rm T}$  of 400 GHz in an ultrascaled InAlN/GaN HFET with a gate length of 30 nm  $^{[5]}$ . However, the values of maximum oscillation frequency ( $f_{\rm max}$ ) in the above devices were very low due to the large gate resistance ( $R_{\rm g}$ ) induced by the rectangular gate, limiting its use in practical high-power amplifier applications.

Song et al employed a 30 nm T-shaped gate to reduce the gate resistance ( $R_{\rm g}$ ), and fabricated an InAlN/GaN HFET with  $f_{\rm T}/f_{\rm max}$  of 194/220 GHz<sup>[6]</sup>. Tirelli et al. obtained an InAlN/GaN HFET with  $f_{\rm T}/f_{\rm max}$  of 205/220 GHz using 30 nm Y-shaped gate<sup>[7]</sup>. Using regrown Ohmic contacts, the source-to-drain distance ( $L_{\rm sd}$ ) was scaled to 140 nm by Schuette et al, and the values of source resistance ( $R_{\rm s}$ ), drain resistance ( $R_{\rm d}$ ) and channel resistance ( $R_{\rm i}$ ) were reduced greatly. A recorded  $f_{\rm T}/f_{\rm max}$  of 302/301 GHz was obtained in a D-mode InAlN/GaN HFET with a gate length of 27 nm<sup>[8]</sup>. Our group fabricated a 70 nm T-shaped InAlN/GaN HFET with 162-GHz  $f_{\rm T}$  and 176 GHz  $f_{\rm max}$  using alloyed Ohmic contacts<sup>[9]</sup>. The great improvements in the frequency performance allow the InAlN/GaN HFETs in power-amplifier applications above W-band.

In this work, we report fully passivated InAlN/GaN HFETs with  $f_{\rm T}/f_{\rm max}$  of 170/210 GHz. This high RF performance is enabled by a gate lithography process to fabricate 60-nm T-shaped electrodes while maintaining a closing-300-nm-wide head in order to minimize gate resistance ( $R_{\rm g}$ ). In addition, regrown n $^+$ -GaN Ohmic contacts were adopted to scale the source-to-drain distance ( $L_{\rm sd}$ ) to 600 nm, which reduced the parasitical resistances. The fabricated InAlN/GaN HFETs also show good DC characteristics. The maximum drain saturation current density ( $I_{\rm ds}$ ) reaches a value of 1.89 A/mm at  $V_{\rm gs}=1$  V and a peak extrinsic transconductance ( $g_{\rm m}$ ) of 462 mS/mm is obtained.

#### 1 Experiments

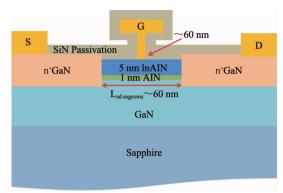

As shown in Fig. 1, the InAlN/GaN heterostructure for this study was grown on (0001) sapphire substrate by metal-organic chemical vapor deposition (MOCVD). Epilayers consist of a 5 nm lattice-matched  $\rm In_{0.17}\,Al_{0.83}\,N$  barrier layer, a 1 nm AlN spacer, and a semi-insulating GaN buffer. As measured using van der Pauw structures at room temperature, the as-grown material produced a 2DEG with a total charge density of  $1.9\times10^{13}~\rm cm^{-2}$  and an electron mobility of  $1.300~\rm cm^2/V\cdot s$ , resulting in a sheet resistance of 253  $\Omega/\Box$ .

Device processing started with mesa isolation, which was performed using a  $\text{Cl}_2/\text{BCl}_3$  plasma-based dry etch-

Fig. 1 Schematic cross section of the InAlN/GaN HFETs 图 1 InAlN/GaN HFETs 器件截面示意图

ing. Subsequently, the InAlN/GaN heterostructure was deposited with SiO<sub>2</sub> mask for n +-GaN ohmic regrowth by plasma enhanced chemic vapor deposition (PECVD) and patterned using reactive ion etching (RIE). A regrowth well-to-well distance (i. e. ,  $L_{

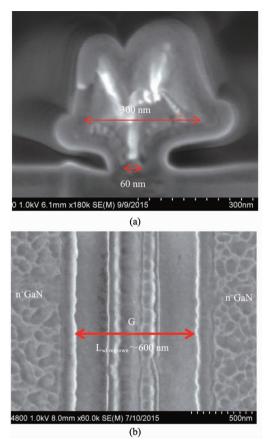

m sd\text{-}regrown}$ ) of 600 nm was defined to reduce the parasitic resistance and capacitance. The n + GaN was regrown by MOCVD with a Si doping level of  $\sim 3 \times 10^{19}$  cm<sup>-3</sup>. The n<sup>+</sup> GaN on top of SiO<sub>2</sub> was lifted off by HF after regrowth. Ti/Au metal stack was deposited as Ohmic contacts. Using the transmission line method (TLM) measurements, the total Ohmic resistance  $(R_{\text{tot}})$  was measured to be 0.38  $\Omega \cdot \text{mm}$ , including metal/n  $^{\scriptscriptstyle +}$ -GaN contact resistance (  $R_{\scriptscriptstyle c}$  ) , n  $^{\scriptscriptstyle +}$ -GaN access resistance between the regrown edge and ohmic metal  $(R_{n+-GaN})$ , and the resistance  $(R_{int})$  at interface of  $n^+$ -GaN/2DEG. In the analysis, all the dimensions of the patterns in TLM were confirmed by SEM. The higher value of  $R_{tot}$  than other reported results is mainly because of a low Si doping level. Moreover, the sidewall obliquity near the regrown interface induced by the plasma dry etching also affects the value of  $R_{\rm int}$ , which further increases the total Ohmic resistance<sup>[10]</sup>. Using a trilayer photoresist, electron-beam lithography was employed to define a 60nm T-shaped gate which is self-aligned to the n + -GaN nonalloyed ohmic contacts. The Schottky gate is in the center of the source-to-drain space. Finally, SiN passivation layer was deposited by PECVD and patterned for contact pads using RIE. Figure 2 (a) shows the cross-sectional scanning electron micrograph (SEM) image of the T-shaped gate for the fabricated InAlN/GaN HFETs. The footprint is conformed to be 60 nm, while maintaining a 300-nm wide head in order to minimize gate resistance. Moreover, as shown in Fig. 2 (b), the distance between the regrown n + GaN contacts is conformed to be 600 nm, while the Schottky gate is in the center between the source and drain contacts.

#### 2 Results and discussion

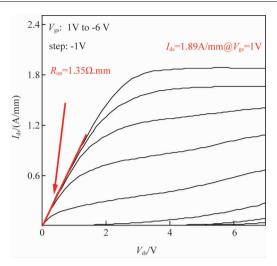

Using a semiconductor characterization system, the DC output characteristics of the fabricated InAlN/GaN HFET were measured and shown in Fig. 3. In the measurements, the drain-source voltage ranges from 0 V to 7 V, with a step of 0.05 V, while the gate bias ranges from 1 V to -6 V, with a step of -1 V. A maximum drain

Fig. 2 Cross-sectional SEM image of the 60-nm T-shaped gate (a), and planform of the fabricated In-AlN/GaN HFET (b)

图 2 (a) 60 nm T 型电镜截面图,(b) InAIN/GaN HFET 器件俯视图

saturation current density ( $I_{\rm ds}$ ) of 1.89 A/mm was obtained at  $V_{os} = 1$  V. The value of on-resistance  $(R_{on})$  for the fabricated device was extracted to be 1.35  $\Omega$  · mm at  $V_{\rm gs}$  = 1 V. This  ${\rm R}_{\rm on}$  value is higher than the total sum of the channel resistance and source/drain resistances ( $R_{\rm s}$ +  $R_{\rm d}$  +  $R_{\rm sheet}$  = 1.21  $\Omega$  · mm) calculated based on the TLM results. The origin of the additional 0.14  $\Omega$  · mm may be due to the effect of gate metal or electric field on the channel electron density, which induces the increase of channel resistance. The high value of drain saturation current density and low value of R<sub>on</sub> are mainly due to the effective scaling of source-to-drain distance. As seen from Fig. 3, the device shows good pinch-off behavior. However, although the ratio of gate length to InAlN barrier layer is larger than 9, some evidence of short-channel effects was observed as can be seen from an increased output conductance at  $V_{\rm ds}$  > 4 V and  $V_{\rm gs}$  < -2 V. This may be a result of the increase of 2DEG electron density under the access region after SiN passivation.

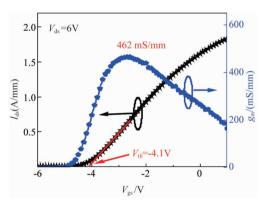

The transfer characteristics of the fabricated InAlN/GaN HFETs are shown in Fig. 4. In the measurements, the drain bias is set as 6 V, and the gate voltage ranges from 1 V to -6 V, with a step of -0.05 V. A peak extrinsic transconductance ( $g_{\rm m}$ ) of 462 mS/mm was obtained at  $V_{\rm gs} = -2.75$  V. The threshold voltage ( $V_{\rm th}$ ) extracted from the transfer characteristics is -4.1 V. Although the

Fig. 3 Output characteristics of InAlN/GaN HFETs with regrown n<sup>+</sup>-GaN contacts 图 3 采用再生长 n<sup>+</sup>-GaN 欧姆接触的 InAlN/GaN HFETs 器件输出特性曲线

scaled device shows high drain saturation current density, the peak transconductance are relatively low at drain bias of 6 V. This is mainly because of the serious short-channel effects induced by the increase of 2DEG electron density under the access region after SiN passivation.

Fig. 4 Transfer characteristics of InAlN/GaN HFETs with regrown n<sup>+</sup>-GaN contacts 图 4 采用再生长 n<sup>+</sup>-GaN 欧姆接触的 InAlN/GaN HFETs 器件转移特性曲线

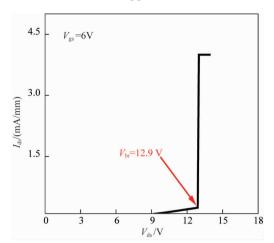

Figure 5 shows the three-terminal breakdown characteristics of the fabricated InAlN/GaN HFETs. During the measurement, the gate bias is set as -6 V while increasing the drain bias. As can be seen from Fig. 5, the off-state breakdown voltage ( $V_{\rm br}$ ) is 12.9 V, indicating the gate – drain breakdown voltage to be 18.9 V. These values correspond to the gate-drain breakdown field of ~ 0.73 MV/cm, which is much lower than the GaN critical field of ~3.4 MV/cm, also lower than the reported one (~3.3 MV/cm) in InAlN/GaN HFETs<sup>[8]</sup>. The leakage current of mesa isolation was  $7 \times 10^{-9}$  A/mm at bias of 15 V, while the leakage current increased to  $7.8 \times 10^{-9}$  A/mm after SiN passivation. This demonstrates that the SiN dielectric shows good insulation. The low breakdown characteristics may be mainly because of the traps at the

interface of SiN/InAlN, which adds leakage channel. In addition, the traps in the GaN buffer will also affect the breakdown characteristic due to the large lattice mismatch between GaN and sapphire substrate.

Fig. 5 The curve of three-terminal breakdown for the InAlN/GaN HFETs

图 5 InAIN/GaN HFETs 器件三端击穿特性曲线

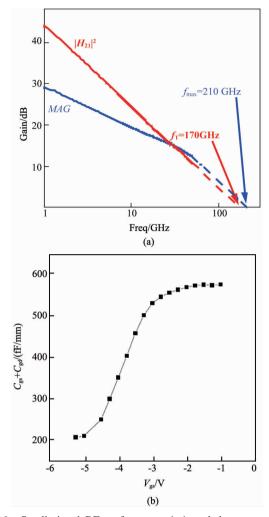

The small-signal RF measurements of the InAlN/ GaN HFETs were carried from 100 MHz to 50 GHz with a 0.05 GHz step using a vector network analyzer. The system was calibrated with an off-wafer line reflect match calibration standard. The measured S-parameters were de-embed using on-wafer open/short calibration structures. [11]. Figure 6 (a) characterizes the current gain  $|H_{21}|^2$  and the maximum available gain (MAG) derived from measured S-parameters plotted against frequency at  $V_{\rm gs}$  of -2.75 V and  $V_{\rm ds}$  of 6 V. Extrapolation of  $|H_{21}|^2$ and MAG -20 dB/dec roll-off yields  $f_{\rm T}$  of 170 GHz and  $f_{\rm max}$  of 210 GHz. To our knowledge, this is a recorded  $f_{\rm T}/f_{\rm max}$  of 170/210 GHz for InAlN/GaN HFETs in domestic. The high RF performance is mainly due to the scaling of source-to-drain distance, which effectively reduces the values of source resistance  $(R_s)$ , drain resistance  $(R_{\rm d})$  and channel resistance  $(R_{\rm i})$ . Moreover, the introduced 60-nm T-shaped gate not only increases the value of  $f_{\rm T}$ , but also reduces the value of  $R_{\rm g}$ , improving the maximum oscillation frequency.

The main extracted equivalent circuit parameters, and comparison of measured and calculated  $f_{\rm T}/f_{\rm max}$

提取的等效电路本征参数,以及 $f_{\rm T}/f_{\rm max}$ 测试值和计算值

|                                          |                                    | max                         |

|------------------------------------------|------------------------------------|-----------------------------|

| 的对比                                      |                                    |                             |

| Intrinsic Parameters                     | Measured $f_{\rm T}$               | Calculated $f_{\mathrm{T}}$ |

| $g_{m,i} = 590 \text{ mS/mm}$            |                                    |                             |

| $C_{\rm gs} = 465  \text{fF/mm}$         | 170 GHz                            | 176 GHz                     |

| $C_{\rm gd} = 68 \text{ fF/mm}$          |                                    |                             |

| $g_{\rm ds} = 84 \text{ mS/mm}$          | $\operatorname{Measured} f_{\max}$ | Calculated $f_{\rm max}$    |

| $R_{\rm i} = 1.15 \ \Omega \cdot \rm mm$ |                                    |                             |

| $R_{\rm g} = 0.30 \ \Omega \cdot \rm mm$ | 210 GHz                            | 208 GHz                     |

| $R = 0.42 \cdot \Omega \cdot mm$         | 210 0112                           | 200 0112                    |

The main intrinsic parameters of equivalent circuit

Fig. 6 Small signal RF performance (a) and the extracted capacitance-voltage characteristics (b) of the prepared InAlN/GaN

图 6 (a) InAIN/GaN HFETs 器件小信号射频特性,(b) 提取 的电容电压特性曲线

obtained from the measured S-parameters are shown in Table 1. The expressions of  $f_{\rm T}$  and  $f_{\rm max}$  can be given as following  $\lfloor 4 \rfloor$ :

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi (G_{\rm m} + G_{\rm m})} \qquad , \quad (1)$$

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi (C_{\rm gs} + C_{\rm gd})} \qquad , \qquad (1)$$

$$f_{\rm max} = \frac{f_{\rm T}}{2\sqrt{(R_{\rm i} + R_{\rm g} + R_{\rm s})g_{\rm ds} + 2\pi f_{\rm T}R_{\rm g}C_{\rm gd}}} \qquad , \qquad (2)$$

where  $g_{\rm m,i}$  is the intrinsic transconductance,  $C_{\rm gs}$  is the

gate-source capacitance,  $C_{\mathrm{gd}}$  is the gate-drain capacitance,  $R_{\rm i}$ ,  $R_{\rm g}$ ,  $R_{\rm s}$ , and  $g_{\rm ds}$  represent the gate-charging, gate, source, and output resistance, respectively. The variations of the extracted values of  $C_{\rm gs}$  +  $C_{\rm gd}$  with gate biases at  $V_{\rm ds}$  of 6 V are shown in Fig. 6(b). The value of  $C_{\rm ss}$  is comparable large due to the thin InAlN barrier layer. Moreover, the thick SiN passivation will also increase the value of  $C_{\rm gs}$ . As shown in Table 1, the calculated values of  $f_{\rm T}$  and  $f_{\rm max}$  show good agreement with the measured ones, respectively. This demonstrates the accuracy of the equivalent circuit model of our device.

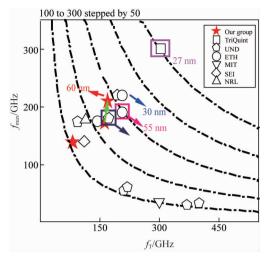

Fig. 7  $f_{\text{T}}$  vs  $f_{\text{max}}$  for the reported InAlN/GaN HFETs 图 7 已报道的 InAlN/GaN HFETs 器件  $f_{\text{T}}$ 和  $f_{\text{max}}$ 汇总图

Some reported results of  $f_T$  vs  $f_{max}$  for the InAlN/GaN HFETs from different groups are summarized in Fig.  $7^{[2.9, 12-15]}$ . Many InAlN/GaN HFETs with  $f_{\rm T}$  above 150 GHz, exhibit the values of  $f_{\rm max}$  less than 60 GHz, resulting in a poor values of  $\sqrt{f_{\rm T} \cdot f_{\rm max}}$  around 100 GHz. The rectangular-shaped gate used in these studies induces a high gate resistance limiting the value of  $f_{\rm max}$ . The value of  $\sqrt{f_{\mathrm{T}} \cdot f_{\mathrm{max}}}$  for our InAlN/GaN HFETs is nearly 200 GHz. The reported values of  $\sqrt{f_{\mathrm{T}} \cdot f_{\mathrm{max}}}$  larger than 200 GHz are obtained with gate length of 30 nm or sun-30 nm. The value of  $\sqrt{f_{\rm T}} \cdot f_{\rm max}$  is the highest one reported for InAlN/GaN HFETs with 60 nm gate length so far. Moreover, the  $f_{\rm T}/f_{\rm max}$  of 170/210 GHz is also very high for InAlN/GaN HFET on sapphire substrate. Figure 8 also shows the development for the InAlN/GaN HFETs of our group. Using alloyed Ohmic contacts, InAlN/GaN HFET with 100-nm T-shaped gate was fabricated, exhibiting  $f_{\rm T}/f_{\rm max}$  of 81/138 GHz. Gate length was then reduced to 70 nm, the values of  $f_{\rm T}/f_{\rm max}$  were improved to 162/176 GHz in an InAlN/GaN HFET with 2-µm source-to-drain space. Regrown n +-GaN Ohmic contacts were employed to scale the source-to-drain distance  $(L_{\rm sd})$  to 600 nm, which effectively reduced the parasitical resistances. The InAlN/GaN HFET with 60-nm Tshaped gate exhibited  $f_T/f_{max}$  of 170/210 GHz. To further improve the RF characteristics, the gate length needs to be reduced. In addition, the Ohmic resistance of the regrown n + -GaN Ohmic contacts is much larger than the reported ones, and needs to optimize the regrowth of n GaN to reduce the resistance.

#### 3 Conclusions

In summary, we fabricated and characterized an In-AIN/GaN HFET with high values of  $f_{\rm T}$  and  $f_{\rm max}$  on sapphire substrate. In order to reduce the parasitical resist-

ance, including  $R_{\rm d}$ ,  $R_{\rm s}$  and  $R_{\rm i}$ , the source-to-drain distance ( $L_{\rm sd}$ ) was scaled down to 600 nm using n $^+$ -GaN Ohmic contacts. In addition, a 60-nm T-shaped gate was fabricated by self-aligned-gate technology in the middle of the source and drain contacts. Due to the scaled source-to-drain distance, the InAlN/GaN HFET showed a high  $I_{\rm ds}$  of 1.89 A/mm @  $V_{\rm gs}$  = 1 V and a peak  $g_{\rm m}$  of 462 mS/mm. On-wafer small-signal RF measurements indicates that the values of extrapolated  $f_{\rm T}$  and  $f_{\rm max}$  for the device were 170 GHz and 210 GHz, respectively. To the best of our knowledge, the values of  $f_{\rm T}$  and  $f_{\rm max}$  are the best domestic reported for InAlN/GaN HFETs.

#### References

- [1] Kuzmík J. Power electronics on InAlN/(In) GaN; Prospect for a record performance [J]. IEEE Electron Device Letters, 2001, 22 (11): 510-512.

- [2] Sun H, Alt A R, Benedickter H, et al. 205-GHz (Al, In) N/GaN HEMTs[J]. IEEE Electron Device Letters, 2010, 31(9): 293-301.

- [3] Lee D S, Chung J W, Wang H, et al. 245-GHz InAlN/GaN HEMTs with oxygen plasma treatment[J]. IEEE Electron Device Letters, 2011, 32(6): 755-757.

- [4] Lee D S, Gao X, Guo S, et al. 300-GHz InAlN/GaN HEMTs with In-GaN back barrier [J]. IEEE Electron Device Letters, 2011, 32(11): 1525-1527.

- [5] Yue Y, Hu Z, Guo J, et al. Ultrascaled InAlN/GaN high electron mobility transistors with cutoff frequency of 400 GHz [J]. Japanese Journal of Applied Physics, 2013, 52(8): 08JN14-08JN14-2.

- [6] Song B, Sensale-Rodrigueza B, Wang R H, et al. Monolithically integrated E/D-mode InAlN HEMTs with f<sub>T</sub>/f<sub>max</sub> > 200/220 GHz[C]. In Device Research Conference, 2012, University Park TX: 1.

- [7] Tirelli S, Marti D, Sun H, et al. Fully passivated AllnN/GaN HEMTs with of 205/220 GHz [J]. IEEE Electron Device Letters, 2011, 32 (10): 13641366.

- [8] Schuette M L, Ketterson A, Song B, et al. Gate-recessed integrated E/D GaN HEMT technology with f<sub>T</sub>/f<sub>max</sub> > 300 GHz[J]. IEEE Electron Device Letters, 2013, 34(6): 741-743.

- [9] Han T T, Dun S B, Lv Y J, et al. 70-nm-gated InAlN/GaN HEMTs grown on SiC substrate with f<sub>T</sub>/f<sub>max</sub>160 GHz[J]. Journal of Semiconductors, 2016, 37(2):024007.

- [10] Guo H Y, Lv Y J, Gu G D, et al. High-frequency AlGaN/GaN high-electron-mobility transistors with regrown ohmic contacts by metal-organic chemical vapor deposition [J]. Chin. Physics Letter, 2015, 32 (11) · 118501 (1-3).

- [11] Chen G, Kumar V, Schwindt R S, et al. A low gate bias model extraction technique for AlGaN/GaN HEMTs [J]. IEEE Trans Micro Theory Tech., 2006, 54(7): 2949 2953.

- [12] Sensale-Rodriguez B, Guo J, Wang R H, et al. Comparative study of E- and D-mode InAlN/AlN/GaN HEMTs with  $f_{\rm T}$  near 200 GHz [C]. In ISDRS College Park, 2011, MD, USA.

- [14] Sun H, Alt A R, Benedickter H, et al. Ultrahigh-speed AlInN/GaN high electron mobility transistors grown on (111) high-resistivity silicon with  $f_{\rm T}=143~{\rm GHz}[~{\rm J}]$ . Applied Physics Express, 2010,  ${\bf 3}(9)$ : 094101 (1-3).

- [15] Yue Y, Hu Z, Guo J, et al. InAlN/AlN/GaN HEMTs With Regrown Ohmic Contacts and  $f_T$  of 370 GHz[J]. *IEEE Electron Device Letters*, 2012, **33**(7): 988 990.

- [16] Ma C L, Gu G D, Lv Y J. A high performance InAIN/GaN HEMT with low R<sub>on</sub> and gate leakage [J]. *Journal of Semiconductors*, 2016, 37(2):024009-3.